成果展示

微电子所在“Post-FinFET”纳米线器件集成研究中取得重要进展

近日,微电子所集成电路先导工艺研发中心(十室)在集成电路面向7纳米及以下技术代的“Post-FinFET”器件研究中取得重要进展。

FinFET器件是当前16/14纳米节点集成电路工艺技术的关键架构。由于沟道静电势控制问题,7纳米及以下技术代的研发面临严重的技术挑战。环栅纳米线器件因具有优异的静电完整性和弹道输运特性,被公认为最有希望取代FinFET并应用在7纳米以下节点的理想器件结构。但环栅纳米线器件因其独特的三维悬浮纳米线沟道以及全包围环栅结构,导致难以直接利用现有的准平面工艺实现大规模的产业集成。因此,开发与当前16/14纳米 FinFET主流工艺相兼容的纳米线器件集成技术已成为“Post-FinFET”时代集成电路先导工艺研究的重要方向之一。

在国家科技重大专项02专项项目“16/14纳米基础技术”的支持下,微电子所在主流16/14纳米全后栅高k金属栅FinFET工艺技术研发上取得多项重要成果。十室殷华湘研究员的团队创新性提出了两种纳米线器件集成技术:堆叠准纳米线器件(S-FinFET)技术和替代栅(RMG)中纳米线沟道后释放技术,得到了业界的广泛关注。

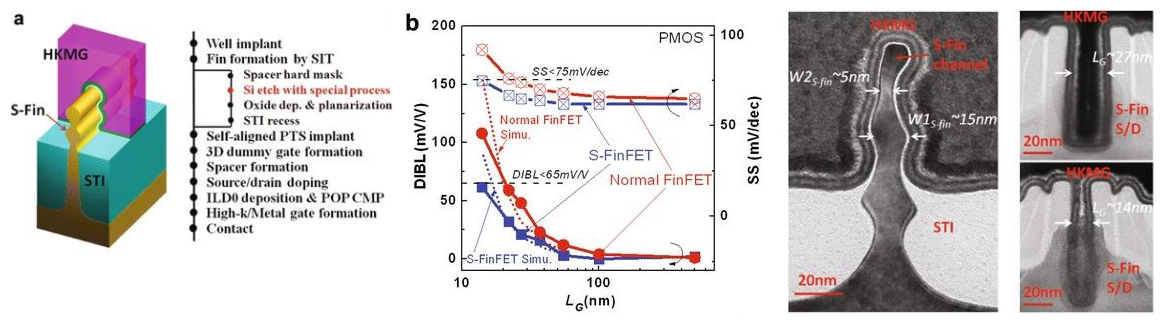

堆叠准纳米线器件(图1)兼具传统FinFET器件的产业化可制造性和类似常规纳米线器件的沟道静电势可控性。科研人员在微电子所先导工艺研发平台上成功制备出最小物理栅长为14纳米的器件,其SS和DIBL参数分别达到75mV/dec和62mV/V,参数分布离散性接近常规FinFET器件。该成果发表在2015年的Nanoscale Research Letter上[1],得到了审阅者的高度推荐,称“有可能成为下代FinFET技术的重要技术之一”。

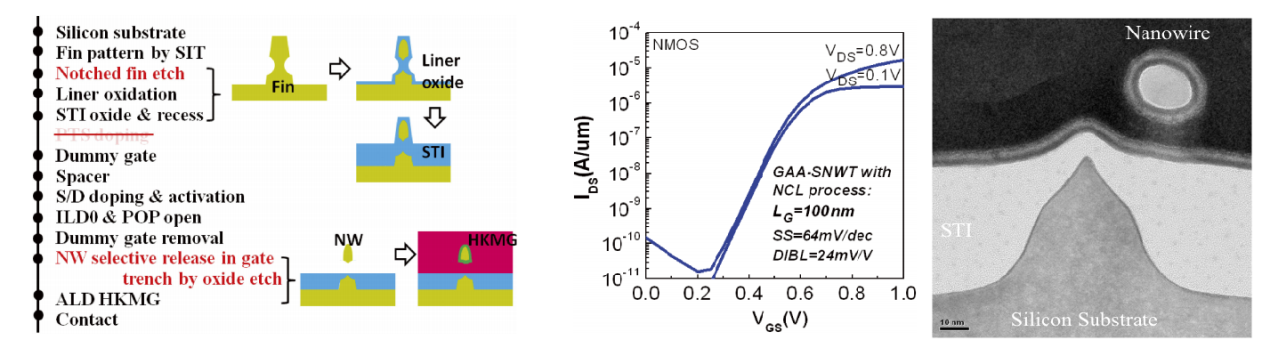

替代栅(RMG)中纳米线沟道后释放技术(图2)突破了长期以来困扰产学研界实现纳米线器件大规模产业集成的工艺限制,最大化兼容现有FinFET基线工艺,实现了高k金属栅的均匀集成并可应用于高密度的电路集成,具有重要的实用价值。该技术在微电子所先导工艺研发平台上成功进行了实验制备,所集成的器件具有接近理想的椭圆形貌沟道及优异的亚阈值特性。该成果在2015年的IEICE Electronics Express上进行了报道[2]。

[1] XU W, YIN H, MA X, et al. Novel 14-nm Scallop-Shaped FinFETs (S-FinFETs) on Bulk-Si Substrate [J]. Nanoscale Research Letters, 2015, 10(1): 249.

[2] MA X, YIN H, HONG P. Gate-All-Around Silicon Nanowire Transistors with channel-last process on bulk Si substrate [J]. IEICE Electronics Express, 2015, 12(7): 20150094-.

图1.堆叠准纳米线(S-FinFET)器件三维结构示意图与集成流程(左);

S-FinFET器件的SS和DIBL参数与常规FinFET器件的比较(中);

成功制备的S-FinFET器件的TEM截面图(右)

图2. 在RMG中形成并释放纳米线沟道的流程示意图,以及制备的器件IdVg曲线和结构TEM截面图。