摩尔定律推动了持续50年的集成电路的发展,然而,时至今日,由于物理极限的限制,晶体管的进一步微缩已经举步维艰。为了进一步增加集成电路性价比,一些基于新原理、新材料、新工艺的晶体管不断被提出,其中负电容场效应晶体管是近年来被广泛研究的对象之一。负电容晶体管可以克服“玻尔兹曼热限制”,即在室温下突破亚阈值摆幅60mV/decade的最低限制,降低电源电压和电路功耗,有望被应用于3nm及以下技术节点。

由于负电容晶体管理论的复杂性,对负电容晶体管以及由其构建的电路特性的理论研究至关重要。近日,中科院微电子所先导中心朱慧珑研究员课题组在英国皇家物理学会《Semiconductor Science and Technology》上发表了文章:Investigation of Device-Circuit for Negative Capacitance Vertical Nanowire FETs Based on SPICE Model

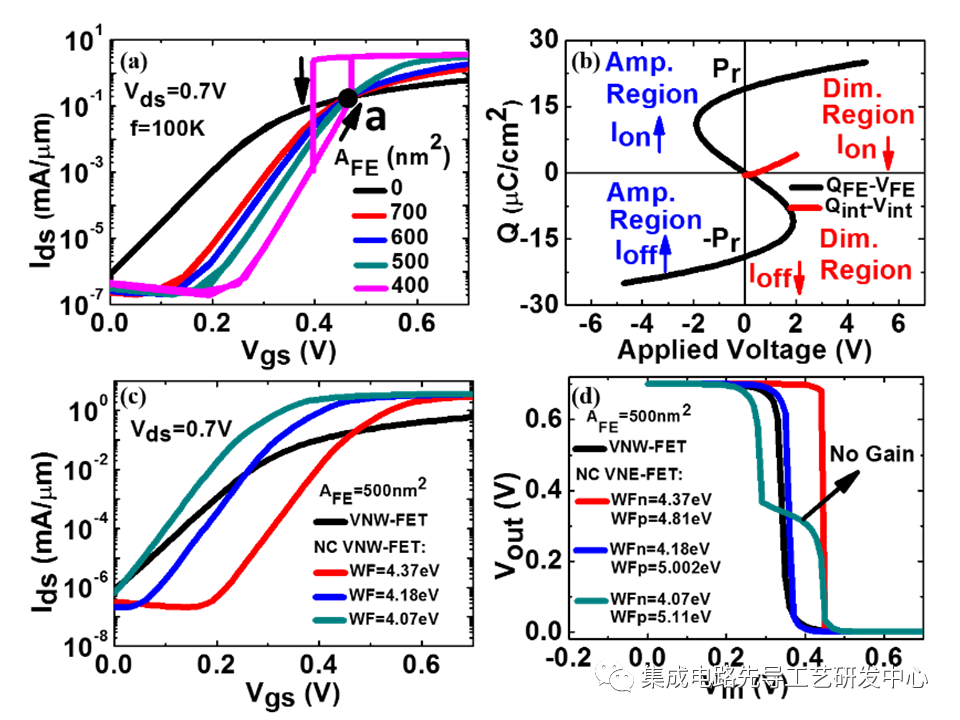

文章中,如图1.(a)中点“a”代表负电容自由能关系中的不稳定点,在该点极化方向开始转变,导致了晶体管电流的增大或减小。因此晶体管阈值电压调节到点“a”位置时,将获得最佳的器件性能。图1.(b)展示了负电容晶体管的四个工作区域,当负电容晶体管工作在第二和第四象限时,将会获得较佳的器件性能。图1.(c)-(d)展示了金属栅功函数对负电容晶体管以及由其构建的CMOS反相器电路特性的影响。文章指出,当负电容晶体管阈值电压过小时,会造成由其构建的CMOS反相器电路增益的严重损失。因此,对于由负电容晶体管构建的集成电路,需要进行电路和器件的协同设计。

图1.(a)不同负电容面积下的负电容晶体管的Ids-Vgs特性,(b)“S曲线”的四个工作区域,(c)不同金属栅功函数下的负电容晶体管的Ids-Vgs特性,(d)不同金属栅功函数下的CMOS反相器的特性。

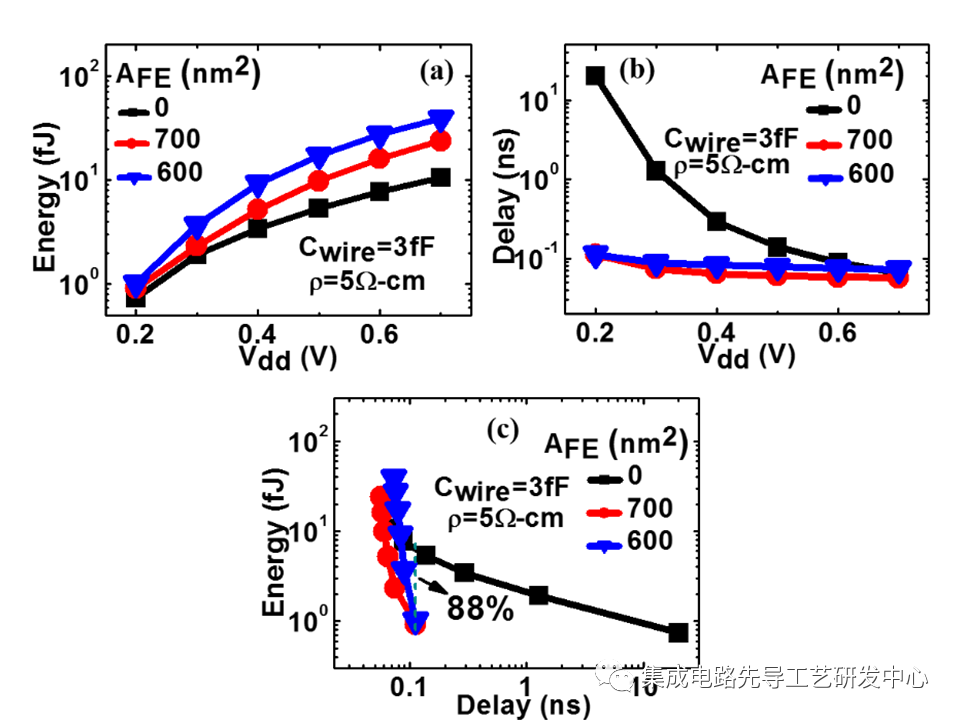

图2.(a)-(c)展示了基于负电容晶体管构建的7阶环形振荡器电路的能量消耗以及传播延时的特性。结果显示,由于负电容晶体管具有更大的栅极电容,因此由其构建的环形振荡器具有更大的动态能量消耗(图2.(a)),然而更大的驱动电流使其拥有更小的传播延时(图2.(b))。此外,通过能量-延时关系分析,在电源电压较小的条件下,电路面积相同时,相同的能量消耗下,负电容晶体管具有更小的传播延时;相同的延时下,负电容晶体管具有更小的能量消耗。

图2. 7

| 相关新闻: |

| 微电子所在先进Co互连阻挡层研究领域取得进展 |

| STT-MRAM器件与集成技术研究 |

学习园地