中科院微电子所近期发表了先导工艺研发中心团队在垂直纳米环栅器件领域获得的最新进展,该类型器件通过在垂直方向构建晶体管结构,大大减少了器件占用面积,在3nm以下先进集成电路制造工艺领域极具应用潜力。

研究背景

GAA晶体管由于沟道由栅极完全包围而具有更好的沟道控制和静电性能而被产业界赋予厚望,行业集成电路制造龙头都前后公布了相关技术的规划。与传统水平沟道的晶体管结构相比,名为vertical GAA FET的垂直GAA晶体管器件(暂译名)由于其沟道方向变为垂直,在器件结构设计时,沟道长度和源漏接触区的面积占用不再那么难以解决,但是相应的,要实现这样的结构对制造工艺提出了严峻的挑战,例如通过刻蚀时间来控制沟道长度的过程变得更加复杂了,在实现路径上,缺乏一种成熟的技术手段来实现从栅极自对准到精准控制沟道长度的过程,而这对于提升芯片性能和可制造性至关重要。

在GAA晶体管发挥作用的领域,器件制造工艺需要原子尺寸级别的大小控制和精确定位排布,原子层刻蚀(ALE,下同)技术众多技术路径中最具潜力实现原子尺度工艺控制的技术之一,但面临工艺时间长等挑战。

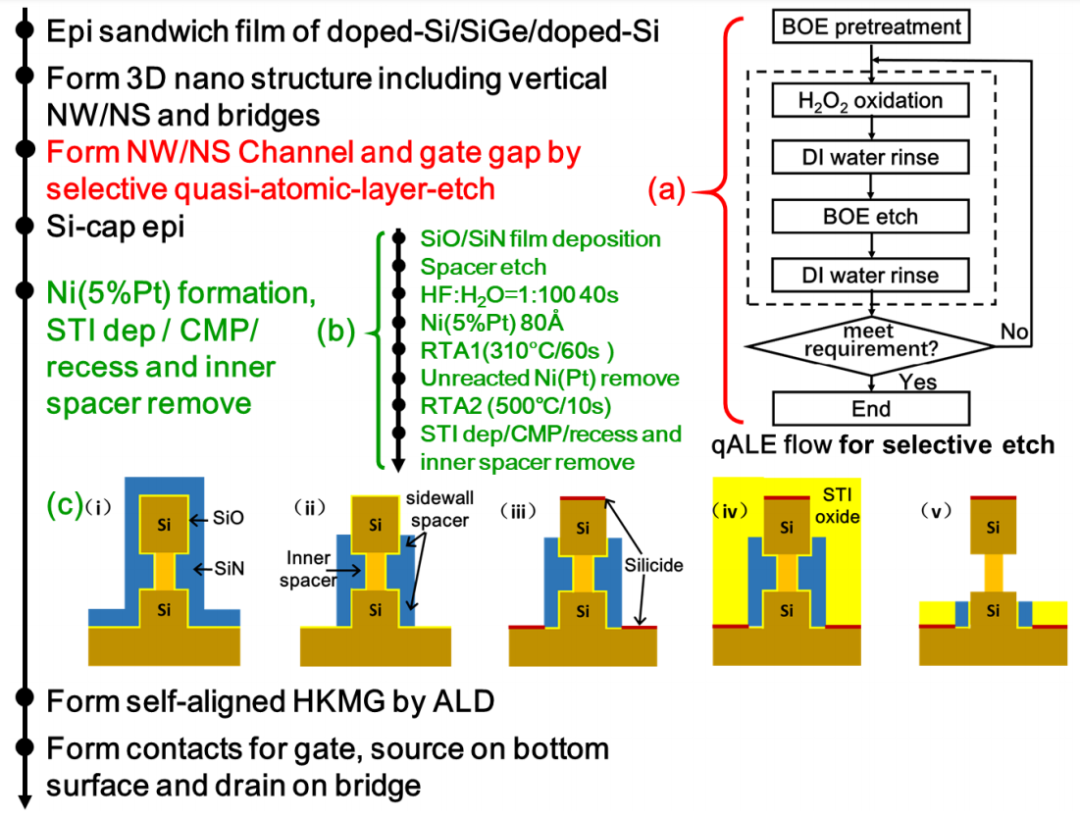

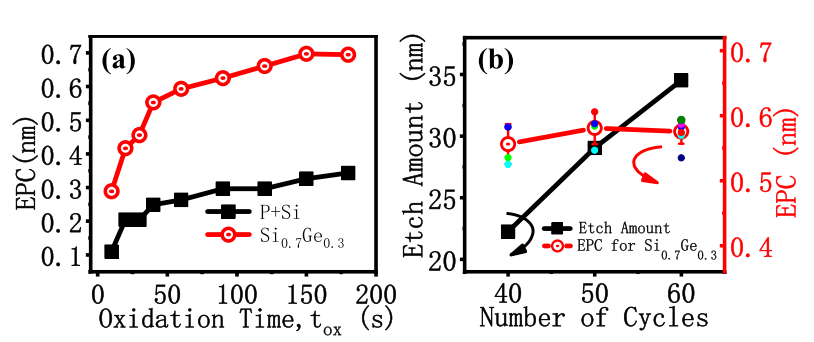

2016年,中科院微电子所集成电路先导工艺研发中心(以下简称“先导中心”)团队提出并设计了一种“三明治”结构的垂直场效应管(vertical sandwich GAA-FETs,简称VSAFETs,下同),并在2019年发表了首个具有自对准栅极的VSAFET*;2020年,报道了锗硅准原子层刻蚀法(qALE,下同)的研究成果*,具有各向同性、对硅选择性等特点。原子层刻蚀法是一种以过氧化氢(H202)和缓冲氧化物刻蚀剂(BOEs)分别作为氧化剂和氧化物去除剂的湿法化学刻蚀工艺。SiGe的qALE具有操作简单、成本低的优点,适用于集成电路制造。

在前述研究基础上,先导中心团队采用与先进CMOS器件集成技术相兼容的工艺制备了VSAFETs,测试了器件性能,并讨论比较了与器件性能相关的沟道锗掺杂比例、金属硅化物工艺、Si-Cap、高温热处理等影响因子,重新调整了VSAFETs的阈值电压。

相关成果以以“Vertical Sandwich GAA FETs With Self-Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process”发表于IEEE Transactions on Electron Devices六月刊,先导中心高级工程师张永奎为该文第一作者,与朱慧珑研究员为共同通讯作者。

*原子层刻蚀,由自限制表面改性和选择性去除改性层两大步骤组成的重复循环的工艺,具有材料表面平坦、深度均匀和原子级的粗糙度可控等优势。

*首个具有自对准栅极的VSAFET:X. Yin et al., IEEE Electron Device Lett., vol. 41, no. 1, pp. 8–11, Jan. 2020. DOI: 10.1109/LED.2019.2954537.

*qALE技术研究成果:X. Yin et al., ECS J. Solid State Sci. Technol., vol.9, no.3, Mar. 2020, Art. no.034012, DOI: 10.1149/2162-8777/AB80AE.

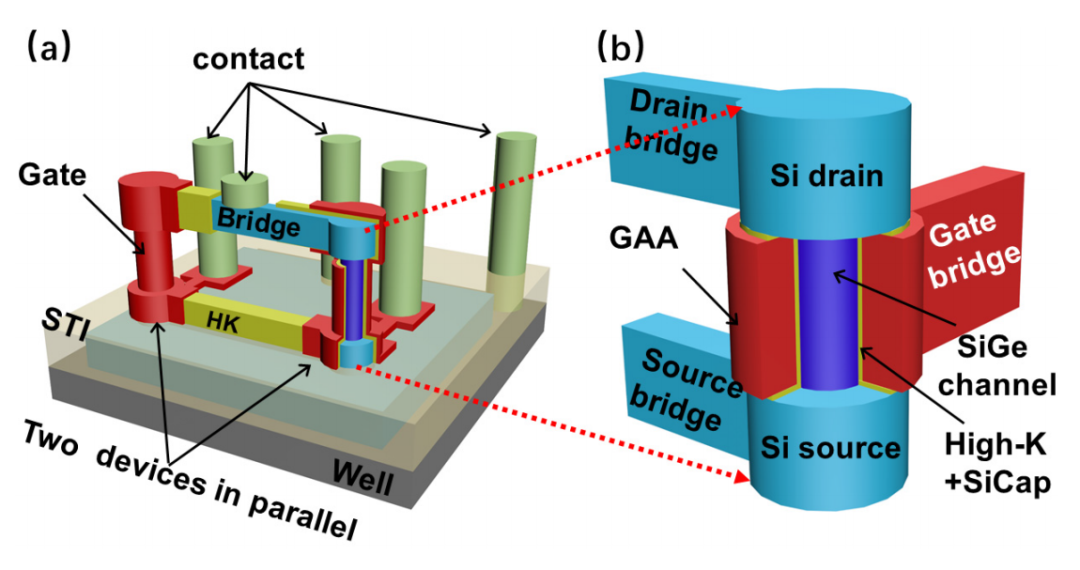

器件结构示意图:整体由两个沿垂直方向平行的晶体管构成

研究内容

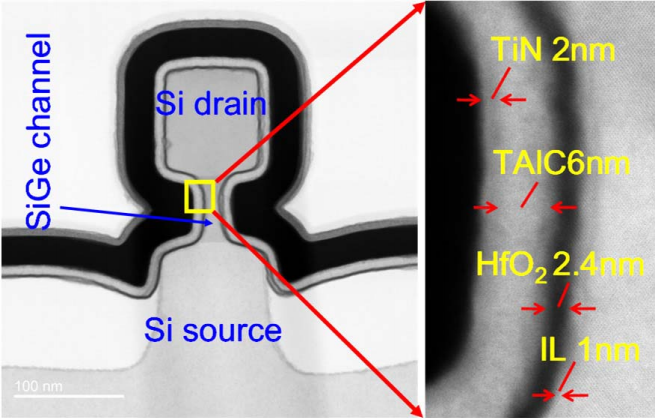

先导中心团队提出并制备了具有自对准高K金属栅、且精确控制有效栅长的pVSAFET器件,系统性研究了各向同性qALE工艺,并将其用于pVSAFET的制备;针对器件样品,研究了VSAFET的特性,以及金属硅化物工艺、Si-Cap、沟道Ge含量和热处理过程等器件性能影响因素:发现较高的热预算*会导致硼离子从漏源区扩散到沟道,导致电性能差;而较低的沟道Ge含量、Si-Cap和TiAlC功函数层有助于提高晶体管阈值电压。

*热预算,thermal budget,表示高温工艺下半导体中某些离子发生扩散的位移长度。

工艺流程

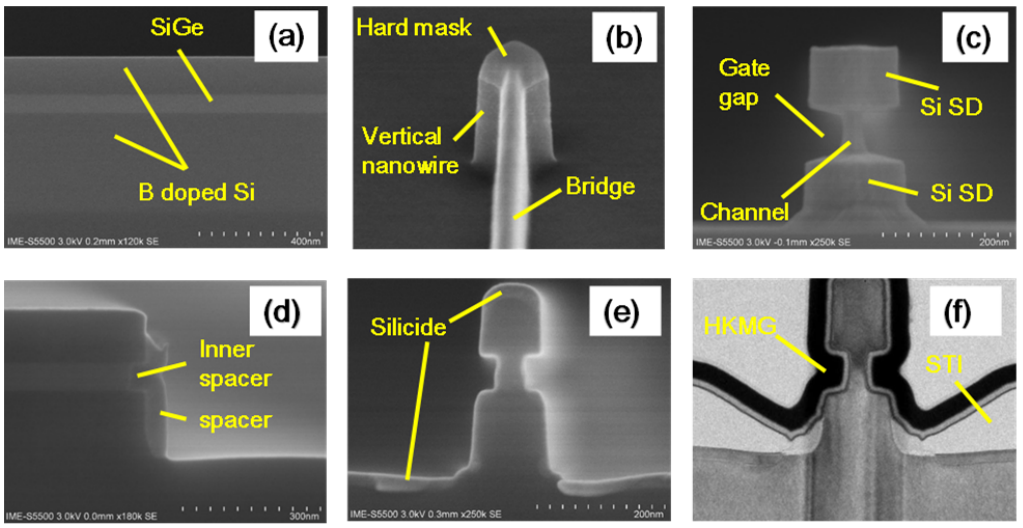

器件形貌图(a-e为SEM图像,f为TEM图像):(a)外延生长后;(b)RIE后倾斜视角3D结构;(c)qALE后;(d);隔离层成型后;(e)金属硅化物工艺后;(f)HKMG沉积后。

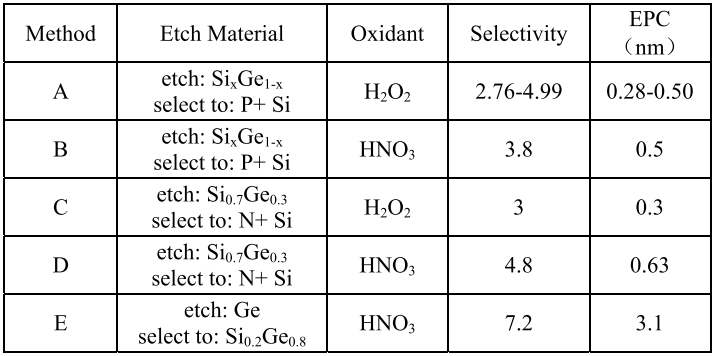

五种qALE工艺方法

循环刻蚀数据采集

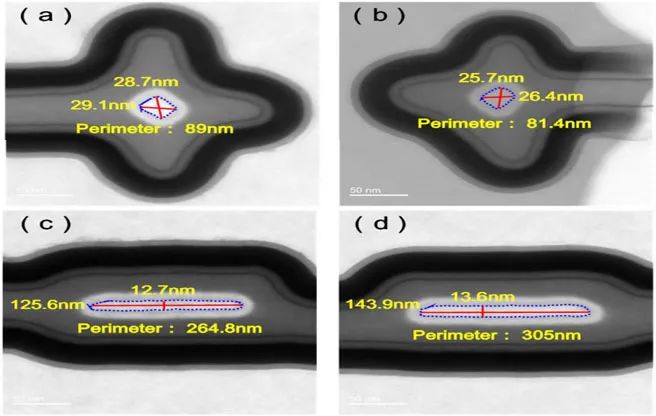

纳米线和纳米片器件TEM俯视图

纳米片器件TEM横截面图

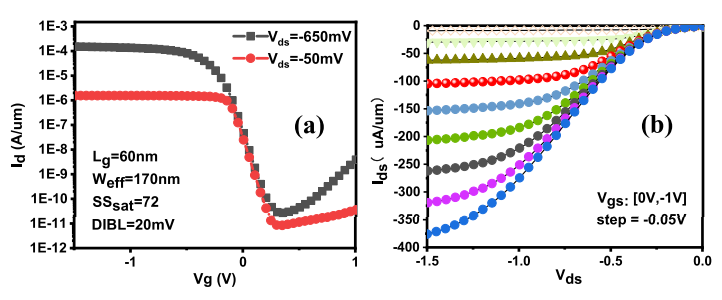

三组I-V特性曲线测试结果:

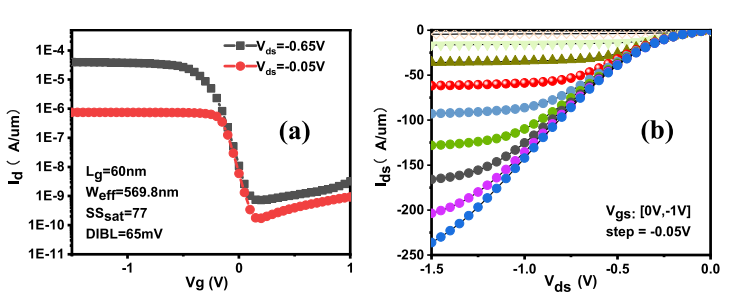

纳米线结构

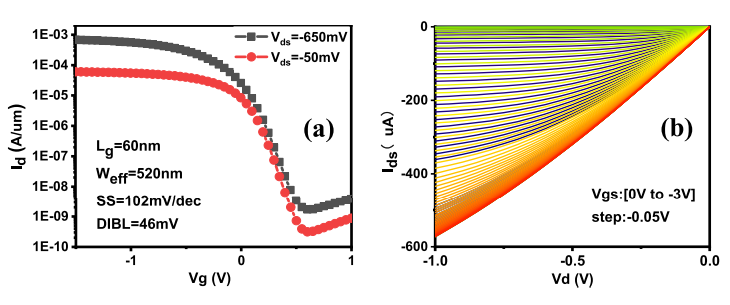

纳米片结构

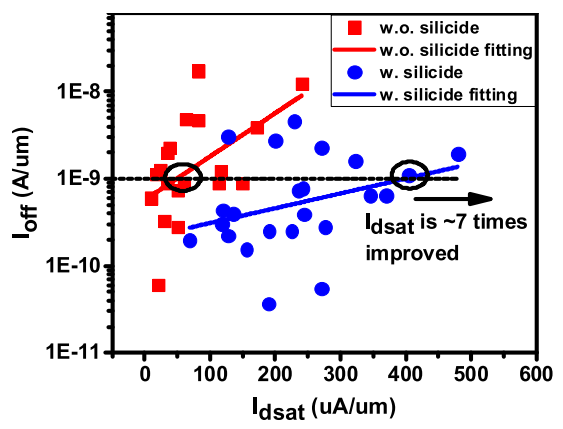

Ioff-Idsat散布图,图中w.o./w.表示without/with可见通过Ni(Pt)硅化物工艺改进后的开关电流提升到7倍

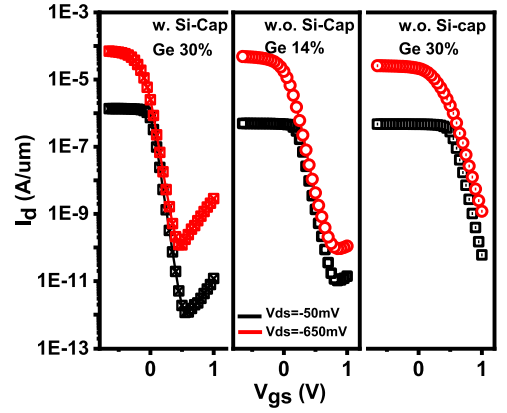

不同Ge组分、有/无Si-Cap工艺条件下Ids-Vgs特性曲线对比

前景展望

垂直纳米环栅器件由于在垂直方向上具有更大的集成自由度和更小的面积占用,通过全新布线方式可以进一步增加晶体管,对于2纳米及以下CMOS逻辑器件和高密度DRAM存储芯片的制造工艺方面具有很大的应用前景,先导中心团队在制造工艺上持续研发,逐渐探明工艺、材料等性能影响因素,加快先导工艺研究进程,推动了原型技术验证,丰实了产业端的技术储备库,也祝愿产业链其他环节早日实现突破,提供良好的技术落地土壤,共同助力建设自主化的集成电路产业链。

团队介绍

朱慧珑,中国科学院微电子研究所研究员、博士生导师,微电子所集成电路先导工艺研发中心首席科学家。1988年获北京师范大学理论物理学博士学位,毕业后曾先后任职于美国阿贡国家实验室、UIUC材料研究实验室、DEC公司、英特尔以及IBM半导体研究和开发中心。归国后先后担任“22纳米关键工艺技术先导研究与平台建设”及“16-14纳米基础技术研究”项目首席专家。曾获国家科技重大专项02专项2010年度“个人突出贡献奖”、IBM半导体研究和开发中心2008年度杰出发明家等多项殊荣,获授权中美发明专利超过300件,发表科技论文50余篇。

中国科学院微电子研究所,前身为原中国科学院109厂,成立于1958年,1986与中科院半导体体、计算技术所与大规模集成电路部分合并,2003年9月,正式更名为中国科学院微电子研究所。微电子所是国内微电子领域学科方向布局最完整的综合研究与开发机构,是国家科技重大专项集成电路装备及工艺前瞻性研发牵头组织单位,是中国科学院大学微电子学院的依托单位,是中国科学院集成电路创新研究院的筹建依托单位。现拥有2个基础研究类中国科学院重点实验室、4个行业服务类研发中心、5个行业应用类研发中心、4个核心产品类研发中心。

中科院微电子所集成电路先导工艺研发中心,国家级研发中心,拥有一条完整的8吋集成电路先导工艺研发线,并兼容硅基光子器件、硅基MEMS器件等集成技术研发;在02专项支持下,先后实现了22纳米CMOS、高 k栅介质/金属栅工程、16/14纳米技术节点的FinFETs、5纳米及以下纳米线和堆叠纳米片器件等关键技术的突破,科研成果首次实现了向国内大型集成电路制造与装备企业的专利技术转移和转化,科研水平迈入世界前列。

| 相关新闻: |

| 微电子所在氧化物栅控离子晶体管方面取得新进展 |

| 微电子所在全线性神经元SOT磁性存储器件研究中取得新进展 |

综合新闻