近日,中科院微电子研究所集成电路先导工艺研发中心王文武/李永亮课题组在锗硅高迁移率沟道器件技术与集成工艺研究领域取得了阶段性进展。课题组提出了一种在三层应变缓冲层(SRB)上外延锗硅材料的技术,并通过锗硅鳍(Fin)刻蚀、新的浅槽隔离(STI)工艺等关键模块研发,成功实现了50%锗硅Fin的导入集成,为锗硅高迁移率沟道三维器件的研制提供了技术基础。

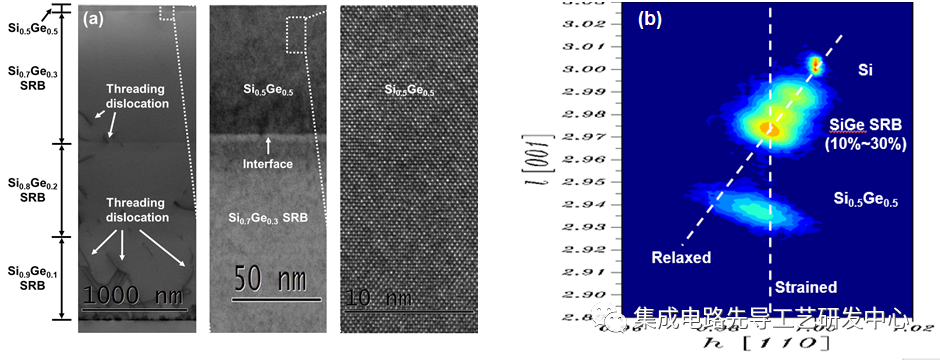

面向集成电路5纳米及以下技术节点,锗硅高迁移率沟道材料因其具有较高的载流子迁移率、更高的器件可靠性以及与现有硅基工艺兼容等特性,成为了新型沟道材料研究的热点。但是,如果直接在Si衬底上外延锗硅材料,其关键厚度将严重限制较高锗含量的锗硅材料制备,从而影响器件电学性能的提升。该课题组提出的三层锗硅SRB结构不仅可以将因晶格失配引起的位错等晶格缺陷完全限制在SRB中,还能直接提升后续鍺硅沟道层的关键厚度。最终,结合平坦化及退火等技术优化,在三层锗硅SRB上实现了表面粗糙度仅为0.23纳米、厚度为50纳米、锗含量为50%的高质量锗硅材料制备。

图1 三层SRB/Si0.5Ge0.5叠层结构

(a)TEM分析,(b)倒易空间应力分析

上述成果以“High crystalquality strained Si0.5Ge0.5

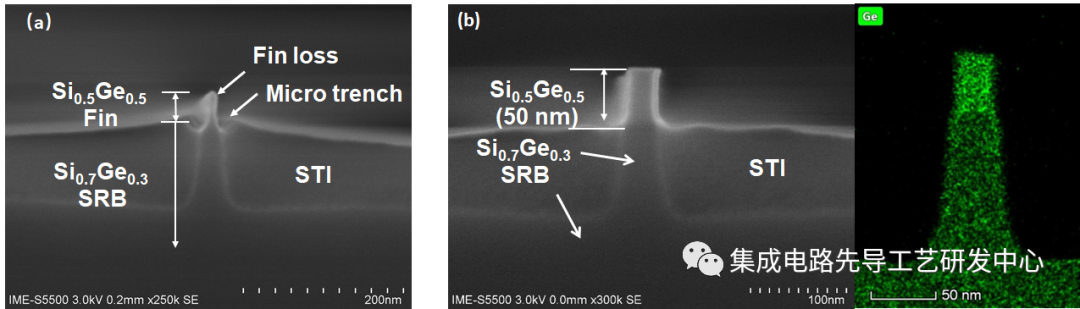

图2 (a)传统STI last方案,(b)优化方案制备获得的三层SRB/Si0.5Ge0.5

上述成果以“Fabricationtechnique of the Si0.5Ge0.5

集成电路创新技术