垂直堆叠纳米线/纳米片全包围栅(Gate All Around, GAA)互补场效应晶体管(Complementary Field Effect Transistor,CFET),将不同导电沟道类型(N-FET和P-FET)的GAA器件在垂直方向进行高密度三维单片集成。相较于现有主流FinFET与水平GAA晶体管集成电路工艺,CFET突破了传统N/P-FET共平面布局间距的尺寸限制,可将集成电路中逻辑标准单元尺度微缩到4-T(Track)高度,同时将减少SRAM单元面积40%以上,在3纳米以下技术代高密度、高性能集成电路制造技术中将成为基础晶体管器件创新架构的有力候选者。

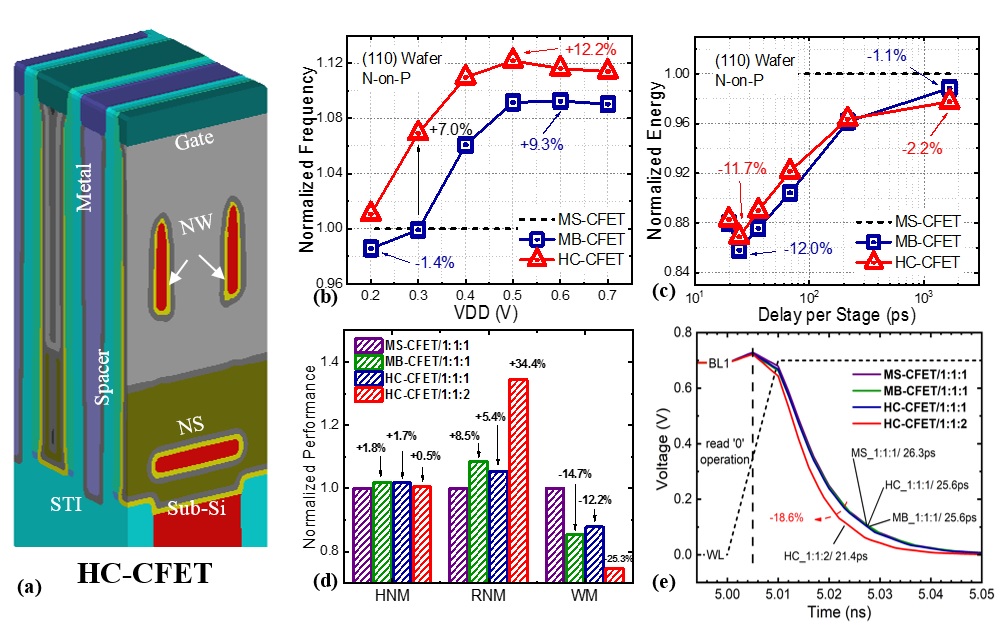

近日,微电子所集成电路先导工艺研发中心殷华湘/吴振华研究团队利用业界主流的Design-Technology Co-optimization(DTCO)方法全面探索了CFET的器件架构优势,提出了新型混合沟道CFET(Hybrid Channel Complementary FET,HC-CFET)结构设计和集成方案。该结构能够在单一衬底上,不借助晶圆键合等混合晶向技术,利用SiNx与SiO2的高刻蚀选择比,通过分步沟道形貌刻蚀,实现对N-FET和P-FET首选高电子与空穴迁移率导电沟道的共同优化,即使得N-FET具有(100)沟道表面晶向,P-FET具有(110)沟道表面晶向,从而在同等投影平面下获得最佳的器件与电路性能。该结构设计与集成方案的可行性已通过Virtual-FAB模拟仿真验证。进一步通过精确数值求解预测了全部寄生参数,对比了不同CFET架构下的17级环形振荡器和SRAM单元性能。结果表明,相较于常规垂直集成Fin和垂直集成纳米片的CFET结构(MS-CFET和MB-CFET),新型HC-CFET具有沟道晶向与空间布局优势,展现出更高的工作频率以及更优的噪声容限窗口,以及在高度微缩的高性能CMOS集成电路应用上的巨大潜力。

该成果近日以“Investigation of Novel Hybrid Channel Complementary FET Scaling Beyond 3-nm Node From Device to Circuit”为题发表在《电气和电子工程师协会电子器件学报》期刊上(IEEE Transactions on Electron Devices 69, 3581 (2022), DOI: 10.1109/TED.2022.3176843),微电子所博士生罗彦娜为该文章第一作者。微电子所殷华湘研究员、吴振华研究员为该文通讯作者。该项研究得到中国科学院“战略重点研究计划”、国家自然科学基金委、北京市科委科技计划等项目的支持。(原文链接:https://ieeexplore.ieee.org/document/9789149)

(a) HC-CFET结构示意图,以及仿真对比的17级环形振荡器(b)归一化频率特性和(c)归一化能耗特性与6T-SRAM单元(d)归一化噪声容限特性和(e)读操作瞬态特性

集成电路创新技术