10纳米以下传统硅基逻辑器件在尺寸微缩道路上面临沟道漏电与迁移率劣化的严重挑战。课题组开展面向大规模集成逻辑电路的新型MOS器件结构与关键工艺技术研究,研究抑制纳米MOS器件短沟道效应并持续提高器件驱动性能的关键技术,同时研究相关物理机制及内在机理,研发在大规模逻辑电路中的应用集成技术,形成成套创新工艺,实现技术向工业界的转移并开展合作开发:

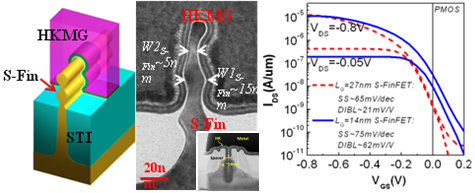

1、开展可大规模集成的异构FinFET与取代栅中硅基纳米线研究:研究兼容传统FinFET技术的半环栅和全环栅器件结构,研究纳米沟道的制造技术,研究纳米沟道的量子输运机理,研究标准单元电路的集成应用。

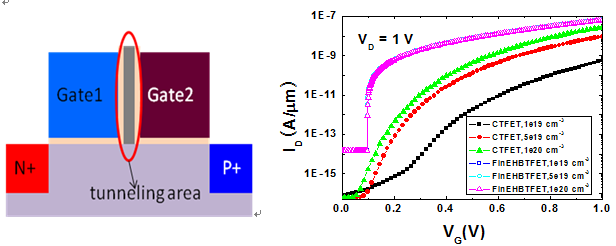

2、开展基于FinFET的超低功耗隧穿晶体管研究:研究兼容传统FinFET工艺的超低功耗隧穿晶体管器件结构,研究集成工艺,研究特殊的工作机理及电路应用方式。

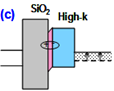

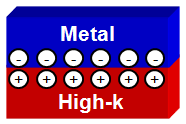

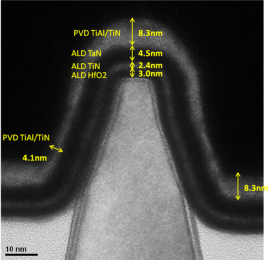

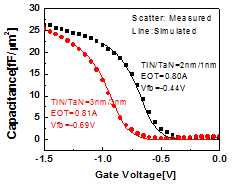

3、开展纳米尺度三维高k金属栅材料与界面工程研究:研究适合10纳米以下超大高宽比的新型多层高k金属栅材料及集成工艺,研究改善栅极与沟道界面质量的物理机制,研究金属栅多阈值技术以及提高器件可靠性的机理与方法。

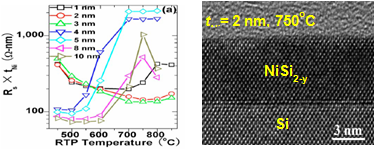

4、开展新型源漏低阻工艺与金属接触技术:研究源漏超低温选择外延技术,研究金属与硅、锗硅、重掺杂衬底等材料的硅化物及直接接触技术,研究形成低阻通道的物理机制及工艺方法,研究电路优化应用。

微电子器件与集成技术研发中心