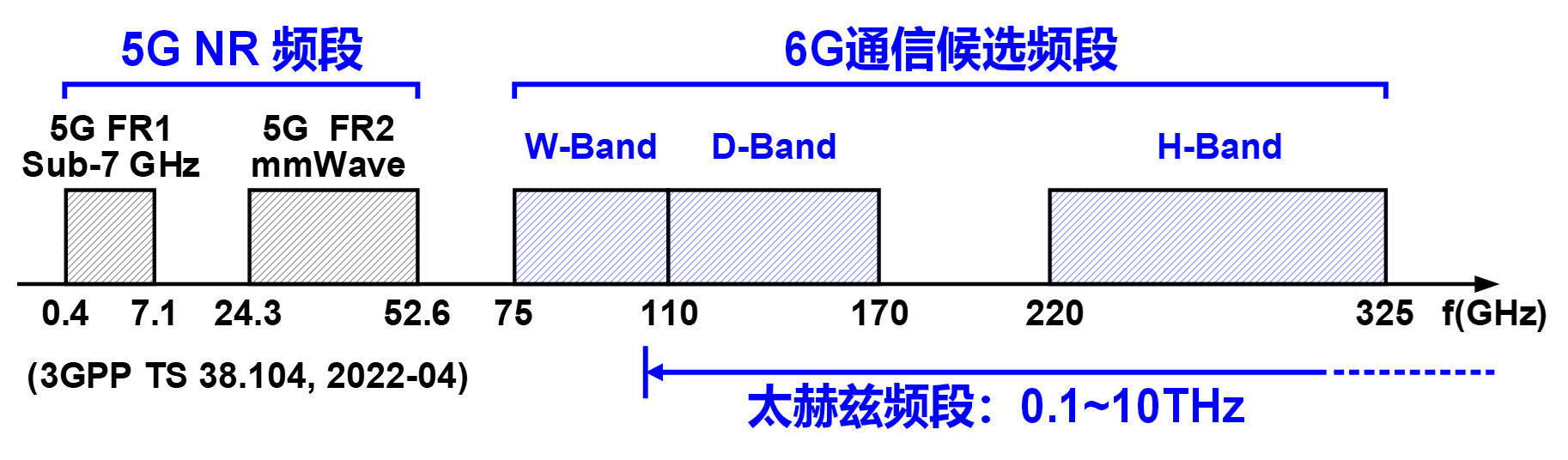

5G NR频段和6G通信候选频段

研究方向

1. 模拟、射频、混合信号集成电路设计

2. 硅基射频、毫米波、太赫兹通信芯片设计

3. 硅基压控振荡器、频率综合器、收发机芯片设计

4. 功率放大器、低噪声放大器、滤波器等射频前端电路设计

招生招聘

本课题组每年招收3-5名优秀硕士、博士研究生,常年招聘模拟、射频、混合信号集成电路设计方向的博士后研究员、助理研究员、副研究员、研究员,同时欢迎本科生加入。详情请附上简历咨询 yangzunsong@ime.ac.cn

课题组负责人

课题组负责人邮箱:yangzunsong@ime.ac.cn

代表性学术成果

论文

[1] Yunbo Huang, Yong Chen, Zunsong Yang, Rui P. Martins, Pui-In Mak,"A 0.027mm2 5.6-7.8GHz Ring-Oscillator-Based Ping-Pong Sampling PLL Scoring 220.3fsrms Jitter and -74.2dBc Reference Spur," IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, Feb. 2024.

[2] Zunsong Yang, Masaru Osada, Shuowei Li, Yuyang Zhu, and Tetsuya Iizuka, "A Reference-Sampling PLL with Low-Ripple Double-Sampling PD Achieving -80-dBc Reference Spur and -259-dB FoM with 12-pF Input Load," IEEE Symposium on VLSI Technology and Circuits (VLSI), Kyoto, Japan, June 2023.

[3] Zunsong Yang, Zule Xu, Masaru Osada and Tetsuya Iizuka, "A 10-GHz Inductorless Cascaded PLL with Zero-ISF Sub-Sampling Phase Detector Achieving -63-dBc Reference Spur, 175-fs RMS Jitter And -240-dB FOMjitter," IEEE Symposium on VLSI Technology and Circuits (VLSI), Hawaii, USA, pp. 10-11, June 2022.

[4] Zunsong Yang, Yong Chen, Shiheng Yang, Pui-In Mak and Rui P. Martins, "A 25.4-to-29.5GHz 10.2mW Isolated Sub-Sampling PLL Achieving -252.9dB Jitter-Power FoM And -63dBc Reference Spur," IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, pp. 270-272, Feb. 2019.

[5] Zunsong Yang, Yong Chen, Pui-In Mak and Rui P. Martins, "A 0.003-mm2 440fsRMS-Jitter and -64dBc-Reference-Spur Ring-VCO-Based Type-I PLL Using a Current-Reuse Sampling Phase Detector in 28-nm CMOS," IEEE Asian Solid-State Circuits Conference (A-SSCC), Macau, pp. 283-284, Nov. 2019.

[6] Zunsong Yang, Yong Chen, Pui-In Mak and Rui P. Martins, "A 0.003-mm2 440fsRMS-Jitter and -64dBc-Reference-Spur Ring-VCO-Based Type-I PLL Using a Current-Reuse Sampling Phase Detector in 28-nm CMOS," IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), vol. 68, no. 6, pp. 2307-2316, June 2021.

[7] Zunsong Yang, Yong Chen, Pui-In Mak and Rui P. Martins, "A Calibration-Free, Reference-Buffer-Free, Type-I Narrow-Pulse-Sampling PLL with -78.7-dBc REF Spur, -128.1-dBc/Hz Absolute In-Band PN and -254-dB FOM," IEEE Solid-State Circuits Letters (SSC-L), vol. 3, pp. 494-497, Oct. 2020.

[8] Zunsong Yang, Yong Chen, Jia Yuan, Pui-In Mak and Rui P. Martins, "A 3.3-GHz Integer-N Type-II Sub-Sampling PLL Using a BFSK-Suppressed Push-Pull SS-PD and a Fast-Locking FLL Achieving -82.2-dBc REF Spur and -255-dB FOM," IEEE Transactions on Very Large Scale Integration Systems (TVLSI), vol. 30, no. 2, pp. 238-242, Feb. 2022.

[9] Yong Chen, Zunsong Yang, Xiaoteng Zhao, Yunbo Huang, Pui-In Mak and Rui P. Martins, "A 6.5 7 m2 0.98-to-1.5mW Non-Self-Oscillation-Mode Frequency Divider-By-2 Achieving a Single-Band Untuned Locking Range of 166.6% (4 to 44 GHz)," IEEE Solid-State Circuits Letters (SSC-L), vol. 2, no. 5, pp. 37-40, May 2019.

[10] Yong Chen, Pui-In Mak, Zunsong Yang, Chirn Chye Boon and Rui P. Martins, "A 0.0071-mm2 10.8pspp-Jitter 4-to-10Gb/s 5-Tap Current-Mode Transmitter Using a Hybrid Delay Line for Sub-1-UI Fractional De-Emphasis," IEEE Transactions on Circuits and Systems I: Regular Papers (TCAS-I), vol. 66, no. 10, pp. 3991-4004, Oct. 2019.

书籍/章节

[1] Hao Guo, Zunsong Yang, Chee Cheow Lim, Harikrishnan Ramiah, Yatao Peng, Yong Chen, Jun Yin, Pui-In Mak & Rui P. Martins, Power-Efficient RF and mm-Wave VCOs/PLL, in Mixed-Signal Circuits in Nanoscale CMOS, Analog Circuits and Signal Processing, Springer, 2023.

抗辐照器件技术重点实验室