微电子所高频高压器件与集成研发中心刘洪刚研究员、王盛凯副研究员带领CMOS研究团队在国家科技重大专项02专项、国家“973”课题和国家自然科学基金等项目的支持下,对high-k/III-V、high-k/Ge界面的缺陷行为及控制方法开展了系统研究,经过近5年的持续攻关,取得了突破性的研究成果。

微电子所高频高压器件与集成研发中心刘洪刚研究员、王盛凯副研究员带领CMOS研究团队在国家科技重大专项02专项、国家“973”课题和国家自然科学基金等项目的支持下,对high-k/III-V、high-k/Ge界面的缺陷行为及控制方法开展了系统研究,经过近5年的持续攻关,取得了突破性的研究成果。

以InGaAs为代表的III-V族半导体材料和Ge材料具有优异的电子和空穴迁移率,其良好的界面有利于显著提升MOS器件的迁移率,是超高速、低功耗CMOS器件的理想沟道材料。然而,由于high-k/InGaAs、high-k/Ge的界面稳定性较差,在界面处存在大量缺陷形成的载流子散射中心,阻碍了迁移率的提高,严重影响了器件的最终性能。

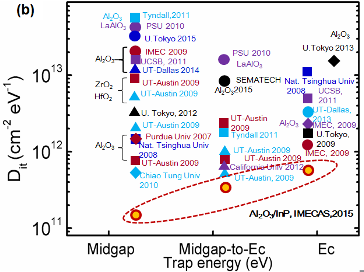

针对这一核心问题,CMOS研究团队创新性地在high-k/InGaAs界面插入极薄外延InP层,将high-k/InGaAs的界面缺陷有效推移至high-k/InP之间。通过采用多硫化氨[(NH4)2Sx]对InP进行表面钝化处理并结合低温原子层高k介质沉积技术,有效抑制了在介质沉积以及金属化后退火过程中的表面氧化和磷原子脱附效应,成功将high-k/InP界面的最低缺陷密度降低至2×1011 cm-2eV-1((图1(a)),有效克服了high-k/III-VMOS电容积累区频散这一普遍性难题,达到世界领先水平(图1(b))。

图1.(a)采用低温ALD工艺结合表面硫钝化技术的high-k/InPMOS电容的电容—电压曲线及界面态密度分布,(b)high-k/InP的界面的Dit低于2×1011cm-2eV-1,达到了世界领先水平

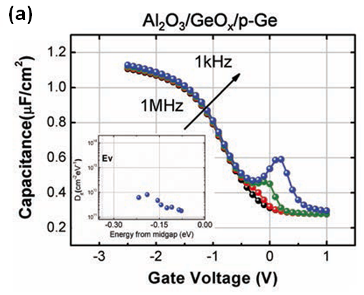

与III-V族沟道不同,在high-k/Ge界面适当引入GeOx层有助于降低界面缺陷密度。由于GeO在420度以上高度环境下会发生明显的脱附现象,进而导致界面性能严重退化,因此,高温常压(400-550度)热氧化方法不适合GeOx界面层的形成。CMOS研究团队提出在原子层高k介质沉积过程中,循环利用臭氧进行低温(300度)原位臭氧氧化,抑制了GeO的高温脱附,同时有效借助了高k介质沉积过程中对臭氧分子的阻挡作用,获得了高质量极薄GeOx界面层。通过该方法,成功将high-k/Ge界面的最低缺陷密度降低至2×1011 cm-2eV-1以下,达到了世界先进水平(图2),同时,光学和电学表征证实,在低温臭氧处理过程中,介质漏电以及介质内部的缺陷数量均得到有效降低,为Ge-MOS器件应用提供了解决方案。

图2.(a)采用原位循环臭氧氧化技术的high-k/GeMOS电容的电容—电压曲线及界面态密度分布,(b)high-k/Ge界面的最低Dit低于2×1011cm-2eV-1,达到了世界先进水平

上述研究成果得到了化合物半导体领域权威杂志“Compound Semiconductor”的持续关注,王盛凯副研究员受邀为该杂志撰写了题为“Turbo Charging the Channel”的专题文章(Feature Article),该成果发表于“Compound Semiconductor”2016年1月/2月刊(图3)。

图3.Shengkai Wang,“Turbo Charging the Channel”,“Compound Semiconductor”,January/February2016,pp.36-44.

http://www.publishing.ninja/V2/page/1839/116/6/1

科研工作