近日微电子所在新型存储器及硬件安全芯片研究领域取得重要进展。刘明院士科研团队两篇研究论文成功入选2020年第40届超大规模集成电路研讨会(Symposium on VLSI)。

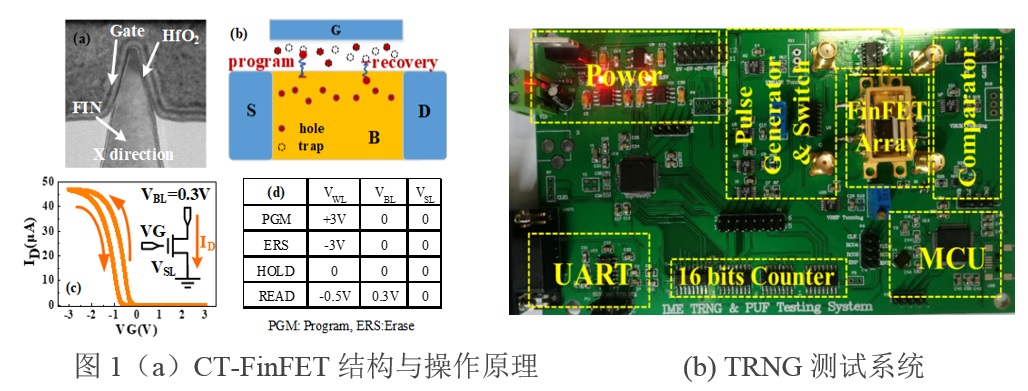

在硬件安全芯片领域,刘明院士/吕杭炳研究员团队展示了一种利用电荷俘获鳍式晶体管(Charge Trapping FinFET,CT-FinFET)器件短期阈值电压恢复特征的真随机数发生器(TRNG)芯片(图1)。研究人员创新地设计了一种时间-频率转换电路,将CT-FinFET阈值电压的弛豫时间转变为高速真随机数据流。该TRNG在-10~85℃范围,对幅度高达600mV和频率高达1.5G Hz的功率噪声表现出极大的抗攻击能力。论文展示的TRNG芯片通过了NIST 800-22和NIST 800-90B所有的随机性测试项,是一种非常有潜力面向先进工艺节点的硬件安全解决方案。该项工作被组委会邀请参加今年VLSI Demo Session的展示。

上述研究成果以题为“Robust True Random Number Generator Using Stochastic Short-Term Recovery of Charge Trapping FinFET for Advanced Hardware Security”的论文入选2020 VLSI Technology。微电子所杨建国副研究员和丁庆婷博士为共同第一作者,吕杭炳研究员和刘明院士为通讯作者。

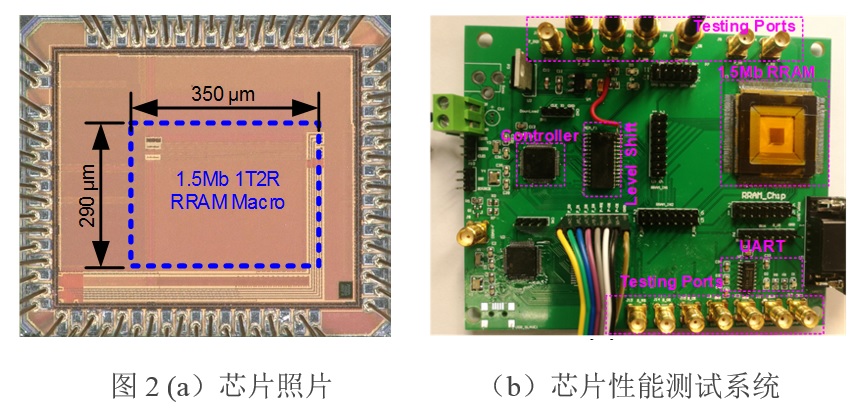

在新型存储器方面,刘明院士/吕杭炳研究员团队与复旦大学薛晓勇副教授合作首次提出了基于PMOS选择器的1T2R 结构RRAM单元,并采用分层位线和三态单元存储技术,使漏电流降低了90%以上。设计了电流精确补偿限流电路和自适应写驱动电路,大幅度提高了阵列的可靠性,同时开发了基于1T2R 自身阵列特点的高速电流型读取电路,实现了极端条件下的高速读取。论文展示了28nm的1.5Mb RRAM测试芯片,将嵌入式NVM 存储密度记录提高了40%,达到14.8 Mb / mm2(图2)。

上述研究成果以题为“A 28nm 1.5Mb Embedded 1T2R RRAM with 14.8 Mb/mm2 Using Sneaking Current Suppression and Compensation Techniques”的论文入选2020 VLSI Circuit。微电子所杨建国副研究员为第一作者,吕杭炳研究员和复旦大学薛晓勇副教授为通讯作者。

刘明院士团队在RRAM方向的研究工作始于2005年,在基础物理、器件结构、电路设计等方向进行了系统深入的研究。研究团队于2015年开始先后与国内主要代工厂中芯国际、华力微电子及上海集成电路研发中心合作开发嵌入式RRAM的量产技术,在中芯国际28nm工艺平台、华力40nm工艺平台上开发了成套RRAM单元结构与集成技术,为在先进工艺节点上设计新一代低功耗、高性能SOC芯片提供了重要的技术平台,相关成果已经开始和终端企业合作推进产业化。在RRAM高密度三维集成方面,刘明院士团队提出了可与3D NAND相媲美的垂直三维集成架构,在国际上率先成功研制了4层(2015年 IEDM)与8层(2017年 IEDM)RRAM三维堆叠阵列,相关研究工作被国际同行列为近五十年来RRAM发展历史中重要事件之一。

相关工作得到国家自然基金委、科技部重点研发计划、中国科学院B类先导专项等项目的支持。

背景介绍:

VLSI与ISSCC(国际固态电路会议)、IEDM(国际电子器件会议)并称微电子技术领域的“奥林匹克盛会”,VLSI是超大规模集成电路和半导体器件领域里最顶尖的国际会议之一,是展现IC技术最新成果的重要窗口。据组委会介绍,今年VLSI收到了创纪录数量的投稿,而论文录用率创历史新低。器件与工艺方向,微电子所作为大陆唯一论文入选单位;电路设计方向,大陆也仅有两篇论文入选(另外一篇为浙江大学与德克萨斯大学奥斯汀分校合作论文),这也是微电子所电路工作的首次入选。

综合信息