近日,微电子所刘明院士科研团队研究成果成功入选2021年第68届国际固态集成电路会议(ISSCC 2021)。这是微电子所首次以第一作者单位在集成电路设计领域最高级别会议上发表论文。

高密度嵌入式非易失性存储器(eNVM)在消费电子、自动驾驶汽车、工业控制和物联网边缘设备等领域的SOC芯片中需求非常大。尽管当前嵌入式NOR闪存仍是主流,但其工艺复杂、集成成本高、难以扩展到28纳米以下节点。阻变存储器(RRAM)以其良好的可微缩性、低功耗和与逻辑工艺良好的兼容性成为一种很有前途的先进工艺节点下嵌入式非易失存储器。但当前先进工艺节点下嵌入式RRAM仍然存在一些挑战,限制了其在eNVM中的实际应用。

本研究主要通过电路设计手段解决先进工艺节点RRAM遇到的以下几个关键问题:第一,由于RRAM的工作电压大于标准电压以及写入路径上会产生一定的电压降,因此需要较高的电源电压,进而产生了电压传输的可靠性问题。第二,写入路径上的电压降随写电压与外围电路的距离而显著变化,这导致了存储单元编程电压的波动。第三,业界应用广泛的自动切断写电路方案,在写电压突然切断后,无法形成致密稳定的导电细丝(CFs),影响了单元的可靠性。第四,以往使用较少高阻/低阻冗余单元产生读参考信号的方案,在遇到单元失效时,由于参考信号偏离很大,导致读取电路无法正常工作。

刘明院士科研团队基于多年在RRAM领域的技术积累,首次设计完成了一颗14纳米 FinFET工艺下的RRAM测试芯片。为应对先进工艺节点RRAM的设计挑战,团队开发了多项创新性的电路技术:通过引入深N阱技术,对P衬底施加适当的偏压降低了高压传输的困难;优化设计了RRAM阵列结构,在阵列的顶部和底部分别非对称的放置位线和源线驱动器,以减小近区和远区单元工作电压的IR降变化,从而实现了写电压的均匀性分布;写驱动电路设计中,基于测试结果,深入分析了不同形式写驱动电路对阻变存储器可靠性的影响规律,提出了一种自适应延迟终止电路(SADT),帮助生成健壮稳定的CFs;读参考信号产生电路中,设计了多冗余可动态配置的1T1R单元结构产生了自动跟随温度、电压及工艺波动的读参考信号,解决了由于少数单元的失效而导致电路无法正常工作的情况。

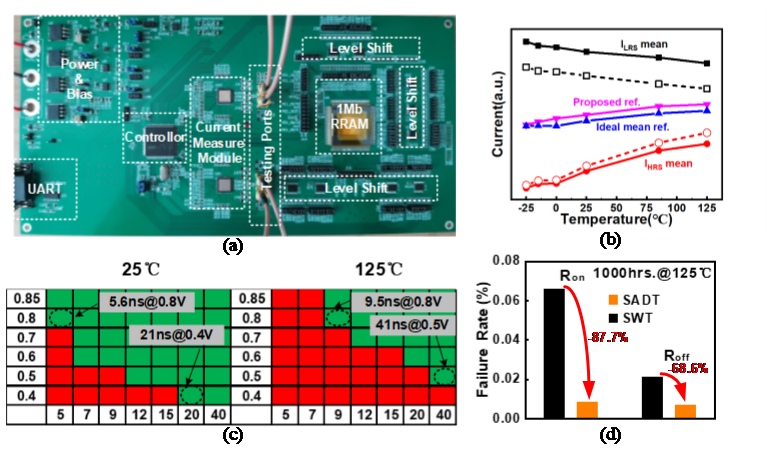

测试结果表明,该芯片具有良好的性能,所设计的电路能够可靠稳定的工作。芯片在0.8V电压下,[-40,125]℃下实现了<10ns的读取时间。该芯片还可以在VDD低至0.4V、室温下可靠地进行读取操作。SADT电路提高了RRAM单元1个数量级的写稳定性,且高阻和低阻的数据保持失效率也分别降低了87.7%和68.6%。上述研究成果以题为“A 14nm-FinFET 1Mb Embedded 1T1R RRAM with a 0.022μm2 Cell Size Using Self-Adaptive Delayed Termination and Multi-Cell Reference”的论文入选2021年ISSCC,与IBM、TSMC、Samsung共同在ISSCC的存储器分论坛展示。微电子所杨建国副研究员为论文第一作者。

相关工作得到国家自然科学基金委、科技部国家重点研发计划、中国科学院B类先导专项等项目的支持。

ISSCC(International Solid-State Circuits Conference)国际固态电路会议由IEEE固态电路协会举办,是世界学术界和工业界公认的集成电路设计领域最顶尖的盛会,被认为是“芯片奥林匹克”,是展现IC技术最新成果的重要窗口。

(a)芯片及测试系统照片;(b)自动跟随的读参考信号测试

(c)芯片读性能测试;(d)芯片阵列可靠性测试结果

综合信息