基于IGZO的CAA结构晶体管具有更低的功耗和更高的密度,可通过单片堆叠的方式将DRAM存储单元面积缩小至4F2。但随着器件尺寸的缩小,无序体系相关的由温度变化导致的不含时(TZI)以及偏置温度不稳定性(BTI)问题进一步恶化,相关模型还未得到研究。

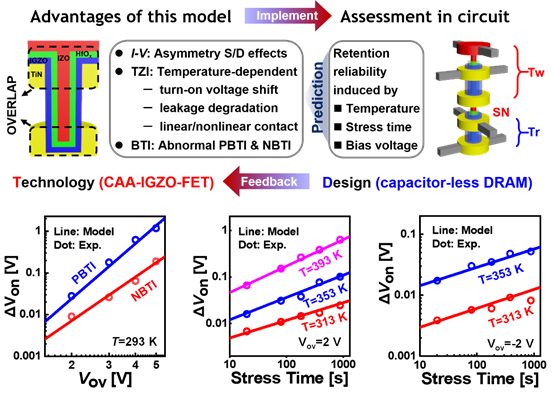

针对上述问题,微电子所重点实验室科研人员基于柱状沟道层的内/外表面电势建立了可堆叠的CAA-IGZO-FET紧凑模型。在器件层级,研究了非对称源/漏的电学行为。在233k ~ 393 K的范围内,考虑了温度对阈值电压、泄漏电流和非线性接触的影响(TZI)。为了进一步研究时间相关的可靠性问题,模型还分析了由PBTI引起的反常的阈值电压的负移。在电路层级,通过将TZI和BTI整合到2T0C DRAM单元中,该模型完成了可靠性感知的设计工艺协同优化流程。

基于该成果的文章“Compact Modeling of IGZO-based CAA-FETs with Time-zero-instability and BTI Impact on Device and Capacitor-less DRAM Retention Reliability”入选2022 VLSI。微电子所博士生郭婧蕊为第一作者,华为孙莹博士为共同一作,微电子所汪令飞研究员、李泠研究员和华为景蔚亮博士为共同通讯作者。

图1. CAA-IGZO-FET模型开发流程及BTI测试

综合信息